ВОВКнОUС, 02 лекция (от 22 февраля)

Материал из eSyr's wiki.

Содержание |

[править] Внутренности вычислительной системы

[править] Подсистема процессор + память

Все в курсе, как устроен процессор фон-неймана. Есть процессор, в нём есть нечто, как его обозвать-то, по-русски оно называется АЛУ. Есть шины. Шины --- нечто, по которому мы можем передавать сигналы. Квадратику с буковкой, допустим P, будем обозначать арифметическое устройство, I --- устройство для подачи команд. При орг. вы. си стемы люди хотят, чтобы эта самая выч. система выдавала могла обрабатывать как можно больше как команд в единицу времени. Достигат ьсяя это может одним способом --- за счёт распараллеливания всяких устройств в составе этой ВС.

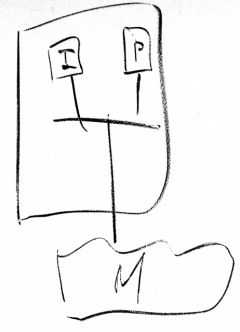

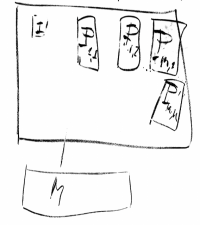

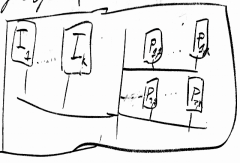

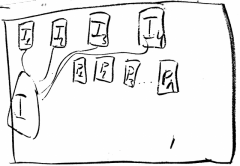

Есть классический процессор, где есть одно I, одно P, рядом есть одно M, то есть память. Где-то есть шина, которая связывает эти понятия. Наиболее части присутствует вот такая картина: у нас есть одно устройство, которе чиатет команды и заставляет эти команды исполнять... наоборот. Внутри процессора может быть неск. сложителей, неск. умножителей, и так далее. Такой подход для массового процессора появился сравнительно недавно, не больше, чем 10 лет назад. Вообще, так делают довольно давно, но на персоналках этостало появляться довольно недавно.Второе, что можно делать. Имеется несколько устройств, которые генерируют команджы для соотв. устройств управления. Вот это вот называется... параллелизм функциональных устройств.

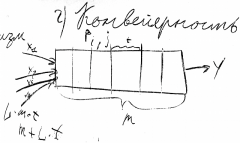

Существует ещё одна точка зрения, на то... есть ещё другая вещь, конвейерность. Получает что-то на входе, и выдаёткакие-то значения. Операция получения значения считаетсч довольно сложная, трудоёмкая, и разбивается на несколько стадий, и каждую можно проводить после предыдущей. Данные подаются на первую стадию, потом на вторую, а первая стадия освобождается, и на первую мы можем опять подать данные. Если бы устройство не было таким... Пусть у нас есть n массивов на L элементом. Если у нас устройство является атомарным, то выход мы получим через m * L, пусть время работы стадии t, получим m * L * t, в случае конвейерности устройства, получим выход через (m + L - 1) * t. Это второй способ.

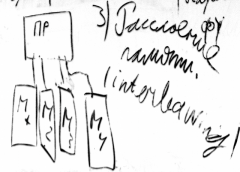

Третий способ. Третий способ связан с тем, что у нас вот эта вот связь между процессором и памятью, она медленная. Тогда делают расслоение памяти. Вся память, которая доступна машине, делится на несколько блоков, к каждому блоку можно обращаться по своему проводу, в результате будет достигнуто некоторое ускорение.

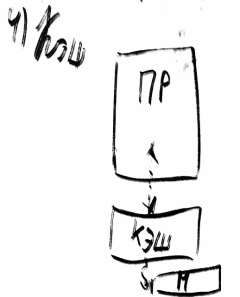

На этом базовые приёмы распределения доступа заканчиваются, и есть ещё способ введения промежуточных хреновин --- использование кэшей.

Кэш ставится между процессором и памятью и работает на более высокой частоте, чем память.

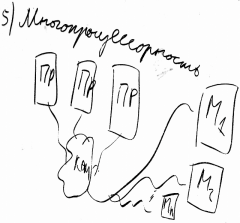

Это вот всякие низкоуровневые приёмы. Есьт приёмы более высокоуровневые. Многопроцессорность.

Следующий уровень --- многомашинность. Когда такие блоки, их может быть много, соединяются через свою коммуникационную сеть.

По способу доступа в память ВС можно классифицировать в несколько классов.

- SMP --- адресное пространство общее, и время обращения к памяти от произвольного процессора одинаковое.

- NUMA --- память общая, время доступа разное.

- MPP --- За каждым процессором закрепляется его собственный кусочек памяти, и доступ к не своей памяти осуществляется через сообщения

- Кластеры

[править] Особенности разных процессоров

На что смотреть, когда выбирается, на основе какого железа нужно выбирать ВС. Нужно примерно выставить себе шкалу присутствующих фишек и цены за эти фишки.

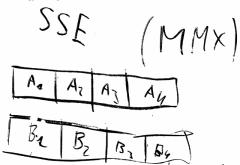

- Intel 32/64/IA-64. Кроме того, есть MMX/SSE. Кроме того, есть HyperThreading. Такая схема вносит гораздо большее число проблем, чем может казаться. В результате получается довольно сложная штука. В результате, разделили АЛУ на две разные кучки. Часть к одному, часть к другому. Также есть два L1-кэша, один кэш L2. И когда нужны данных, кажде из этих являений, называемых ядром, обращается к своему кэшу, потом к общему, и доступ памяти у них общий. Кроме того, есть EM64T

- Itanium. Он связан с VLIW, очень большим инструкционным словом, которое сразу можно загрузить в процессор и которое состоит из нескольких команд. Если раньше независимые УУ, то тут есть ещё главный УУ, который драконит команды, отдавая их дальше.

- Xeon. То же самое, только кэша побольше добавили.

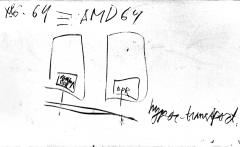

- x86-64 = AMD64. С точки зрения обычного процессора, система команд отличается только наличием дублирующих их 32-битных команд и 64-битных регистров. Кроме того, есть некие отличия: отличия в том, что внутрь процессора добавлен контроллер памяти. Сами процессоры, если их несколько, связаны шиной HyperTransport.

- IBM. У фирмы IBM есть больше количество процессоров. Наиболее инртересные на текущий момент Power и Cell. У Cell есть один главный процессор и 8 SPE. SPE в некоторой степени ущербен. В отличие от ... в общем, там есть один большой управл. процессор а-ля Power, который умеет много разных операий, в частности, обращение в памят ь. SPE такого не умеют, зато они умеют складывать/умножать/делить числа. Cell можно отнести к семейству графических процессоров. Это счастье сейчас стоит в PS3.

- Power. Power 4 (Power 5). Power 4 обладает такой штукой, называется спекулятивное выполнение команд. 8 одновременно исполняемых команд.

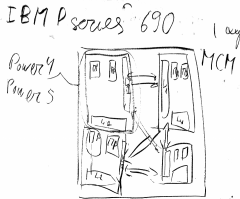

[править] У нас на факультете есть такая штука, IBM p-Series 690

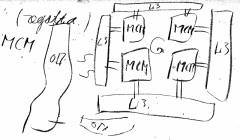

Процессор двухядерный. Кэши связаны некое коммуникационной средой, и сами MCM-модули в количестве 4 штук сажаются в то, что можно условно назвать материнской платой. Кэши третьего уровня связаны с оперативной памятью. Которая тоже расслоена. Такая многоуровневая система позволяет добиться того, что обращние из конкретного процессора в память происходит довольно редко. По возможности, всё это решается внутри кругов и циклов на своём уровне. Соответственно, можно джелать кластеры из регаттт, только очень дорого.

Вопросы организации вычислительных кластеров на основе UNIX-серверов

01 02 03 04 05 06 07 08 09 10 11

Календарь

| пт | пт | пт | пт | пт | |

Февраль

| 15 | 22 | 29 | ||

Март

| 07 | 14 | 21 | 28 | |

Апрель

| 04 | 11 | 18 | 25 |